The line with SEL select sets up SEL as the signal that is evaluated by the when statements that follow. In this code, the with, select and when VHDL keywords are used.

Port ( SEL : in STD_LOGIC_VECTOR (1 downto 0) - select inputĪ : in STD_LOGIC_VECTOR (3 downto 0) - inputsĪrchitecture Behavioral of mux_4to1_top is

MULTIPLEXER 4 A 1 VHDL CODE

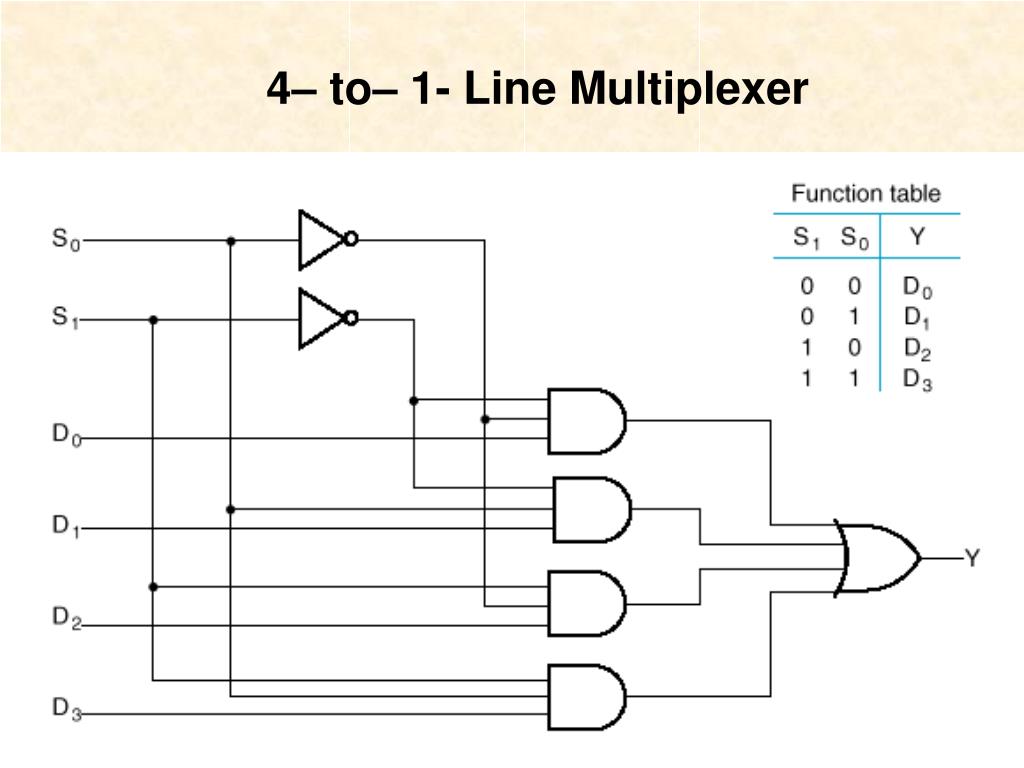

The VHDL code that implements the above multiplexer is shown here. The two SEL pins determine which of the four inputs will be connected to the output.Ġ0 on SEL will connect A(0) to X, 01 on SEL will connect A(1) to X, etc. This video shows the the CPLD with the above code operating.īooks that may interest you: One-Bit Wide 4 to 1 MultiplexerĪ four to one multiplexer that multiplexes single (1-bit) signals is shown below.

A logic 0 on SEL will connect the 4-bit input bus B to the output bus X. The result of this signal assignment is that a logic 1 on SEL will connect the 4-bit input bus A to the 4-bit output bus X. If the condition is false, then the signal to the right of the else (B) will be assigned to the output signal instead (this will occur if the signal on SEL is a logic 0). The when-else construct is a conditional signal assignment construct that assigns the signal on the left of when (A in our example) to the output signal (X in our example) if the condition to the right of when is true (SEL = '1' – if SEL is equal to logic 1). The VHDL when and else keywords are used to implement the multiplexer. The VHDL code for implementing the 4-bit 2 to 1 multiplexer is shown here.Īrchitecture Behavioral of mux_2to1_top is A logic 0 on the SEL line will connect input bus B to output bus X. A logic 1 on the SEL line will connect the 4-bit input bus A to the 4-bit output bus X. We look at two multiplexer examples in this tutorial, the first multiplexes two 4-bit input buses to a single 4-bit output bus, the second example multiplexes four single input lines to a single output line.

0 kommentar(er)

0 kommentar(er)